SDR Block HF

SDR Block HFボードは超長波〜短波帯で送受信できるSDRのトランシーバーボードです。

FPGA内に21個の信号処理回路ブロックを内蔵し、それらはUSBを介して外部のPCから自在に組み替える事が可能です。 その際、FPGAの論理合成やコンフィグは必要ありません。

PCからSDR Block HFボードを制御するには以下で説明するEXCELシート「SDR ASM」を使用します。 VBAマクロでプログラムされており、信号処理回路ブロックの組み換え、波形の取り込み、FFT、AWGデータの転送を行います。

USB通信にはFTDI社のFT232HLを使用しているため、FTDI社提供のAPIを使って容易に自作アプリケーションを作れます。 PC側でのリアルタイム信号処理が可能です。

このボードは様々な受信機、送信器として実験、利用できるだけでなく、回路ブロックを組み替えることでオシロスコープ、スペアナ、サイン波発生(SG)、 任意信号発生(AWG)、その他思いもよらない応用も考えられます。技術者の実験、検証、簡易測定器として、学校などの教材としての利用を想定しています。

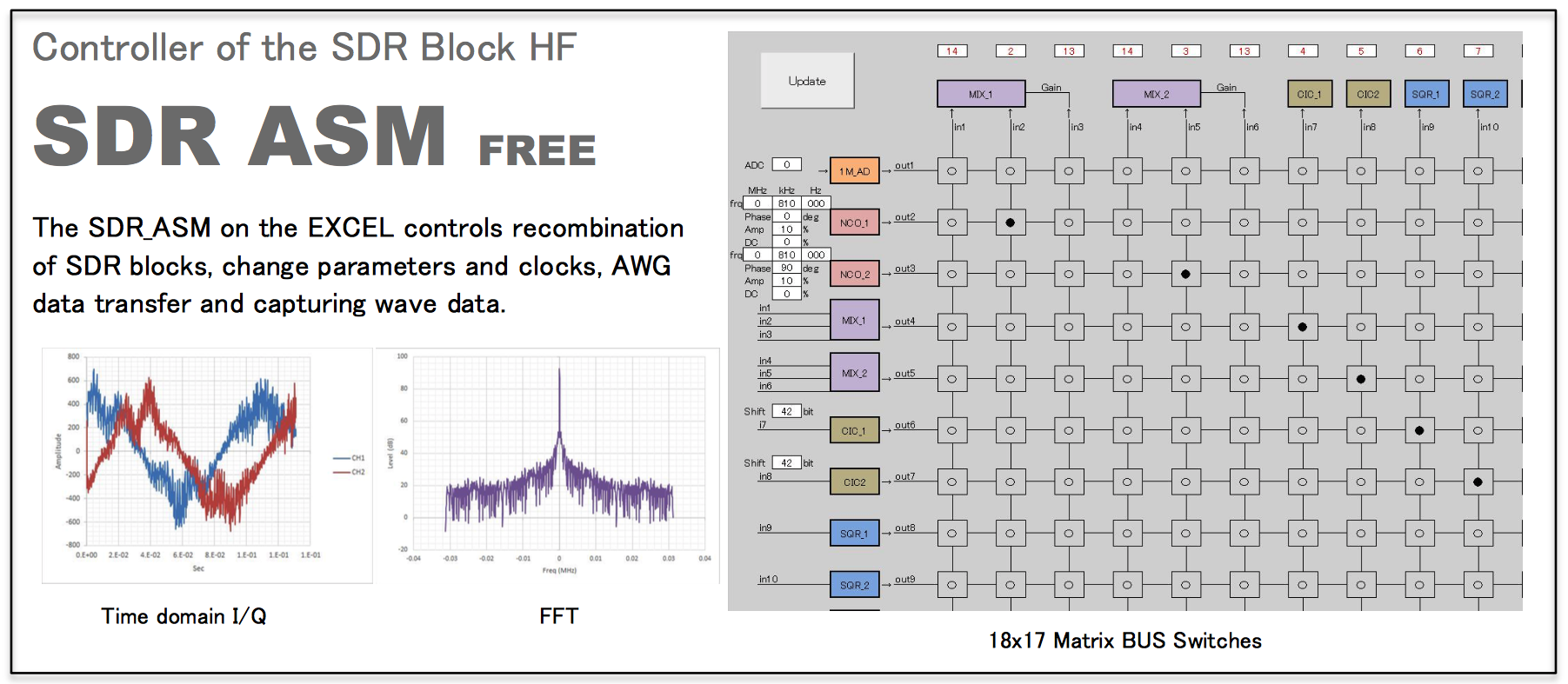

EXCELシート SDR ASM

SDR Block HFボードを制御するEXCELシートです。

FPGA内部の信号処理回路ブロックを自由に組み替える事が可能です。 VBAマクロでプログラムが書かれているためFT232HLのAPIの使い方、SPIコマンドの制御方法など具体的な制御方法を容易に確認できます。

SDR ASMの機能は以下のとおりです。

・バススイッチON/OFF制御による回路ブロックとクロック分配の接続定義

・NCOの発振周波数、位相、振幅、DCオフセットの設定

・CICフィルタのデシメーションレート設定、ゲイン設定

・AWG波形データをPCからFPGAへ転送

・任意ノードの波形取り込みと波形観測(オシロ機能)

・任意ノードの波形取り込みとFFT観測(スペアナ機能)

・各種回路の例題

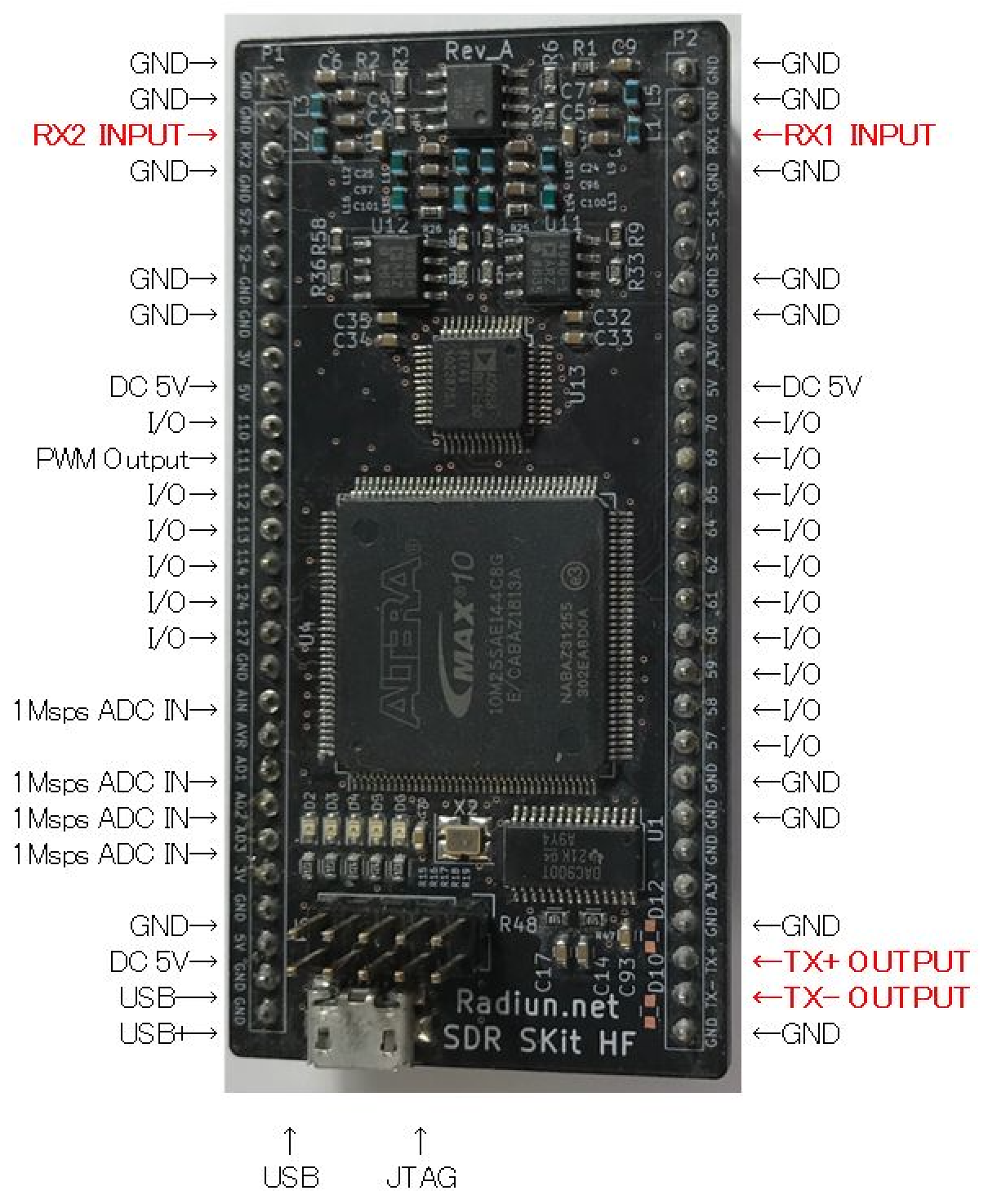

ピン配置と基本性能

| 代表値 | 備考 | |

| 送受信周波数範囲 | 10kHz〜32MHz | IQ変復調可能なのは16MHz以下 |

| 設定周波数分解能 | 5Hz | NCOの最小分解能 |

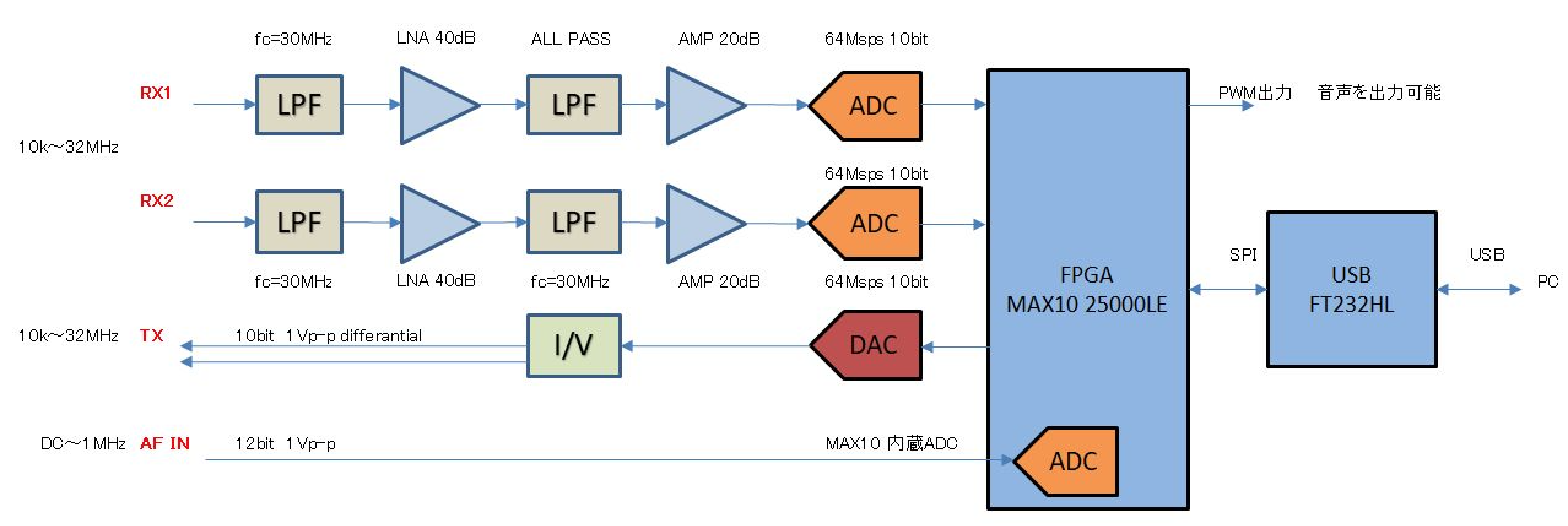

| RX ADC x2ch | 10bit 64Msps | AD9218 65Msps |

| AF ADC x1ch | 12bit 1Msps | MAX10内蔵 |

| TX DAC x1ch | 10bit 64Msps | DAC900E |

| TX出力 | 差動1Vp-p | 無負荷時 |

| RXゲイン | 60dB | LNA LMH6626 40dB |

| 回路ブロック数 | 21個 | 2018/8現在 |

| インターフェイス | USB 2.0 | FT232HL 〜12Mbps |

| 電源電圧 | 5V 500mA | USBによる電源供給 |

| 基板サイズ | 75 x 35 mm | DIP 56pin |

ブロック図

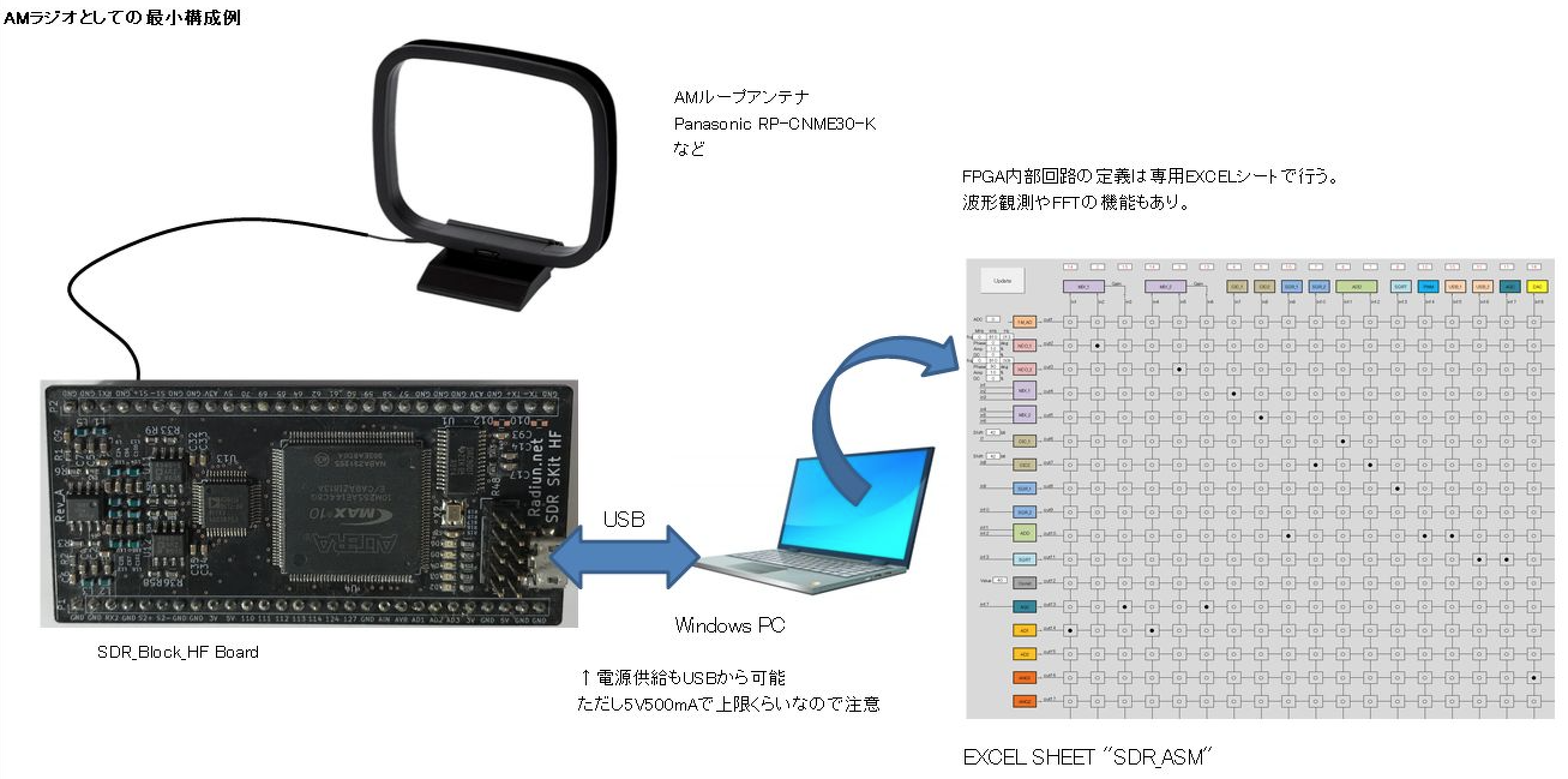

最小構成例

音声はボードからPWMで直接出力できます。ヘッドホンを駆動できるレベルなのでアンプ内蔵スピーカーを使用するのが最も簡単です。

信号処理回路ブロック

| 名称 | 個数 | 機能 | 備考 |

| NCO | 2 | 5Hz〜32MHz正弦波発生 | 位相、振幅、DCオフセット可変 |

| MIX | 2 | 乗算回路 | ゲイン調整可能 |

| CIC | 2 | フィルタ | デシメーションレート可変 CIC4段 |

| SQR | 2 | 自乗回路 | 主に絶対値を得るために使用 |

| ADD | 1 | 加算回路 | 2信号加算1信号出力 |

| SQRT | 1 | 平方根回路 | 自乗された信号を元に戻すため使用 |

| Const | 1 | 定数発生 | DCオフセット、ゲイン固定値のため使用 |

| AGC | 1 | 自動利得制御 | 時定数可変、積分回路 |

| RX AD | 2 | 10bit 64Msps | 60dBアンプされた高速AD |

| AF AD | 1 | 12bit 1Msps | MAX10内蔵、オーディオ入力を想定 |

| AWG | 2 | 任意波形発生 | 12bit 4096ワード、サンプリング可変 |

| PWM | 1 | オーディオ出力 | 11bit 62.5ksps |

| USB | 2 | 波形取り込み | ストリームデータ対応 |

| DAC | 1 | 10bit 64Msps | 主に送信、内部波形観測に使用 |

上記回路ブロック21個は全てFPGA内部に組み込まれています。

今後、機能追加、ブロック追加を継続的に実施し、ダウンロードできるようにする予定です。

構成例_AMラジオ

EXCELシート「SDR ASM」のマトリックス状の結線は全ての配線を定義可能ですが、信号の流れを読みにくいため以下のような例題を準備しています。

AGC付き長波〜短波のAMラジオです。中波なら簡単なループアンテナで十分な感度が得られるため最初の動作確認にはうってつけです。

実用的な受信範囲はIQ信号を扱える16MHz以下になります。

AGC付き長波〜短波のAMラジオです。中波なら簡単なループアンテナで十分な感度が得られるため最初の動作確認にはうってつけです。

実用的な受信範囲はIQ信号を扱える16MHz以下になります。

構成例_DSBラジオ

AGC付き長波〜短波のDSBラジオです。LSB/DSBどちらも受信可能です。SSBとして側帯波をしっかり落としたい場合はPC上の信号処理でFIRのヒルベルトフィルタを使います。

実用的な受信範囲はIQ信号を扱える16MHz以下になります。

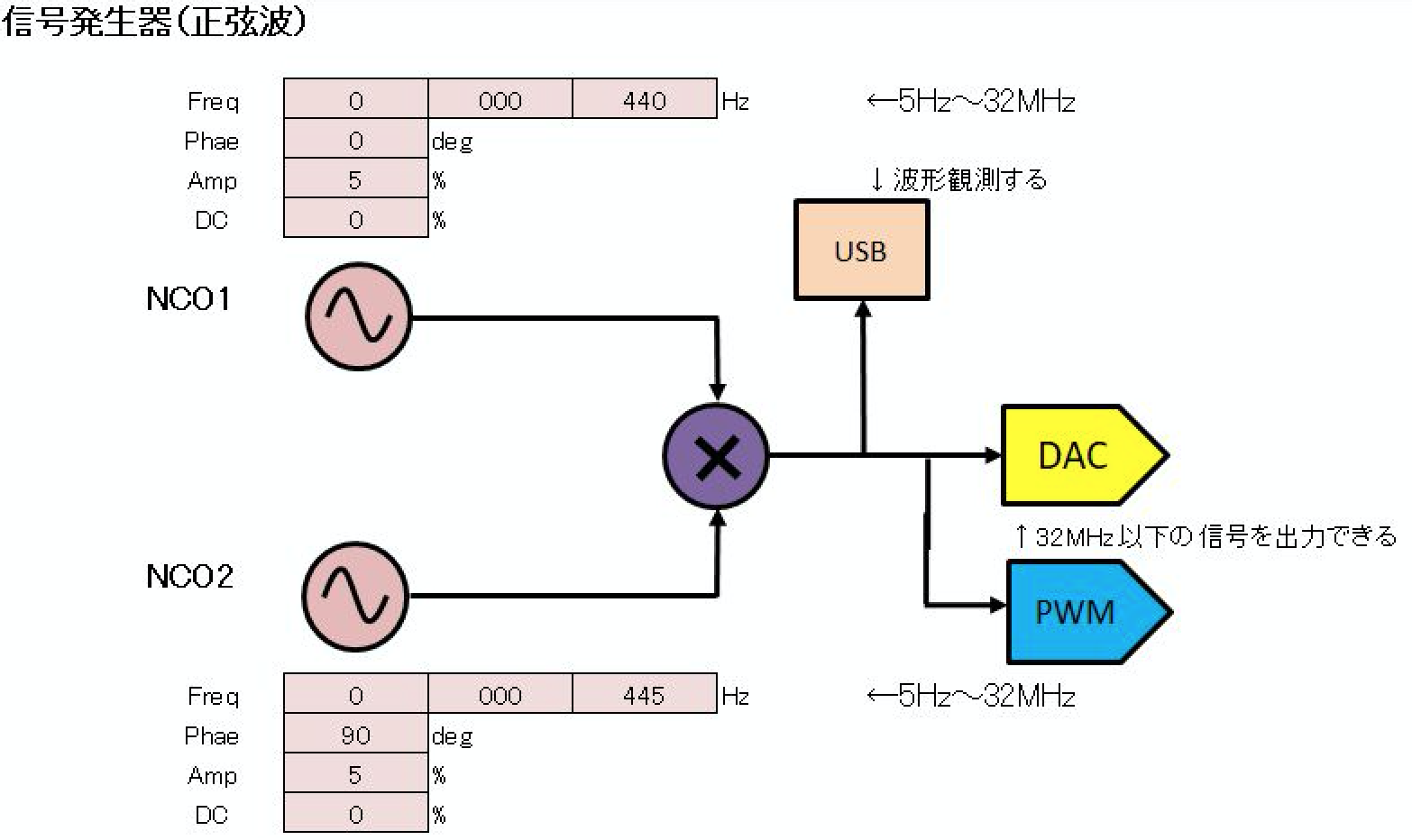

構成例_信号発生器

2種類の異なる周波数をミキシングして2トーン信号を生成しています。

音で確認できるようにNCOは440Hzにしていますが、もちろんMHzの周波数でも可能です。

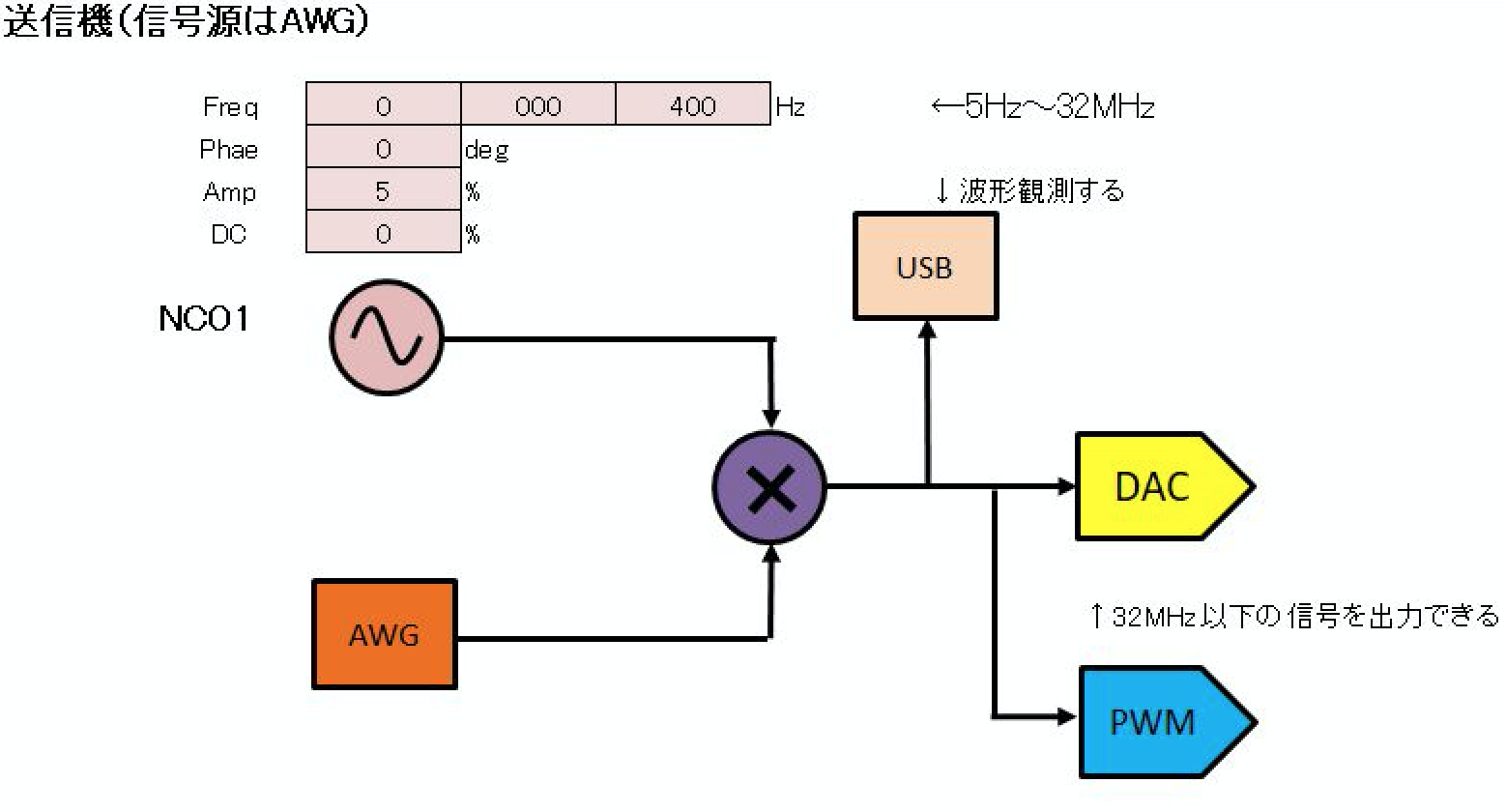

構成例_任意波形発生器

EXCEL上で自由に波形を作りAWGから出力させます。VBAは遅いですが、C言語などでPC上のプログラムを作ればデジタル変調のリアルタイム信号生成などに使用できます。

AWGデータはEXCELシート「SDR ASM」の「AWG」ページからFPGA上のRAMに転送できます。

音で確認できるようにNCOは400Hzにしていますが、もちろんMHzの周波数でも可能です。

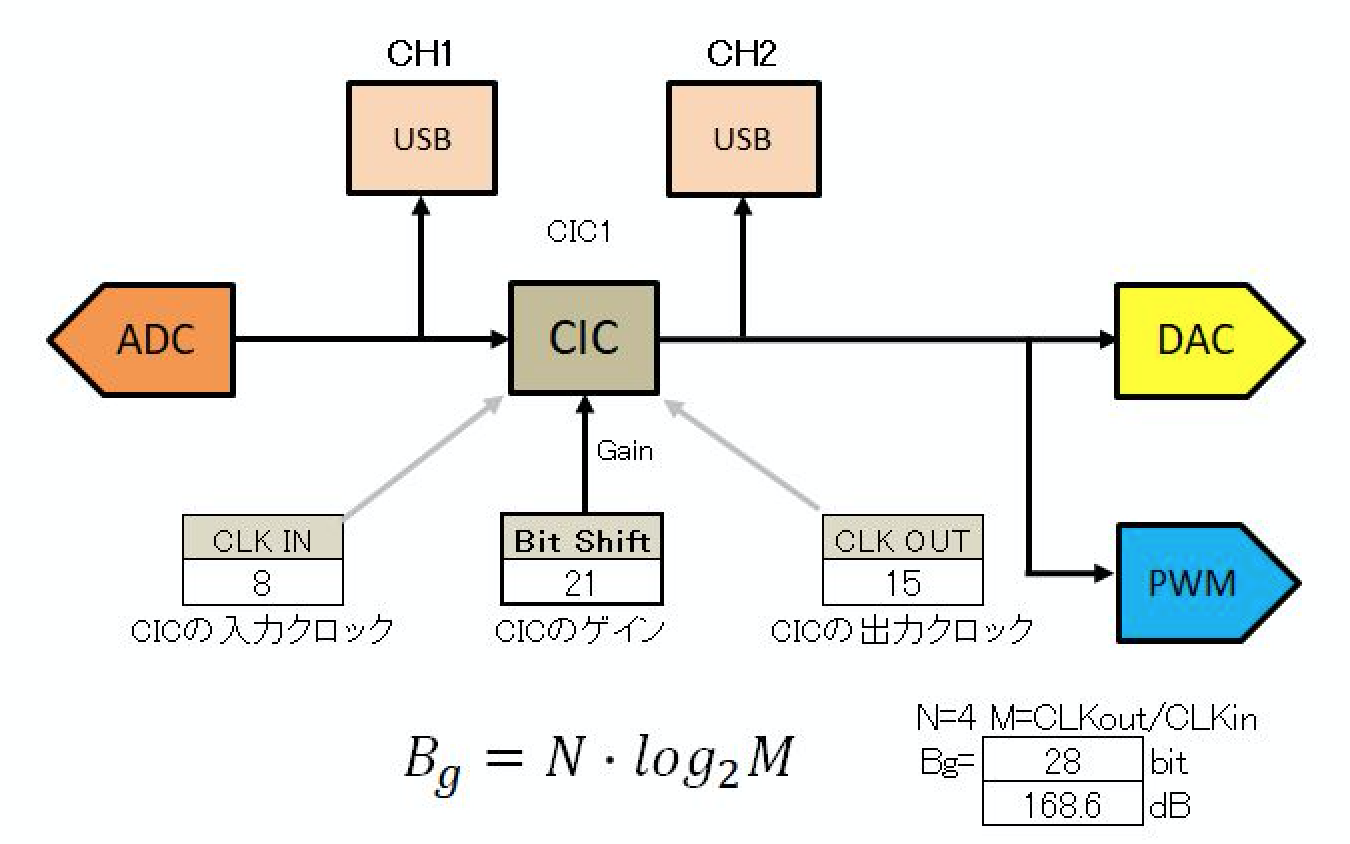

構成例_CICフィルタの実験

動作の理解が難しいCICフィルタを実験できる回路です。

ADC出力のホワイトノイズを入力し音を聞きながらデシメーションレートを変更すると一瞬で音色が変わるため理解のスピードが上がります。これまでのFPGAでは不可能でした。

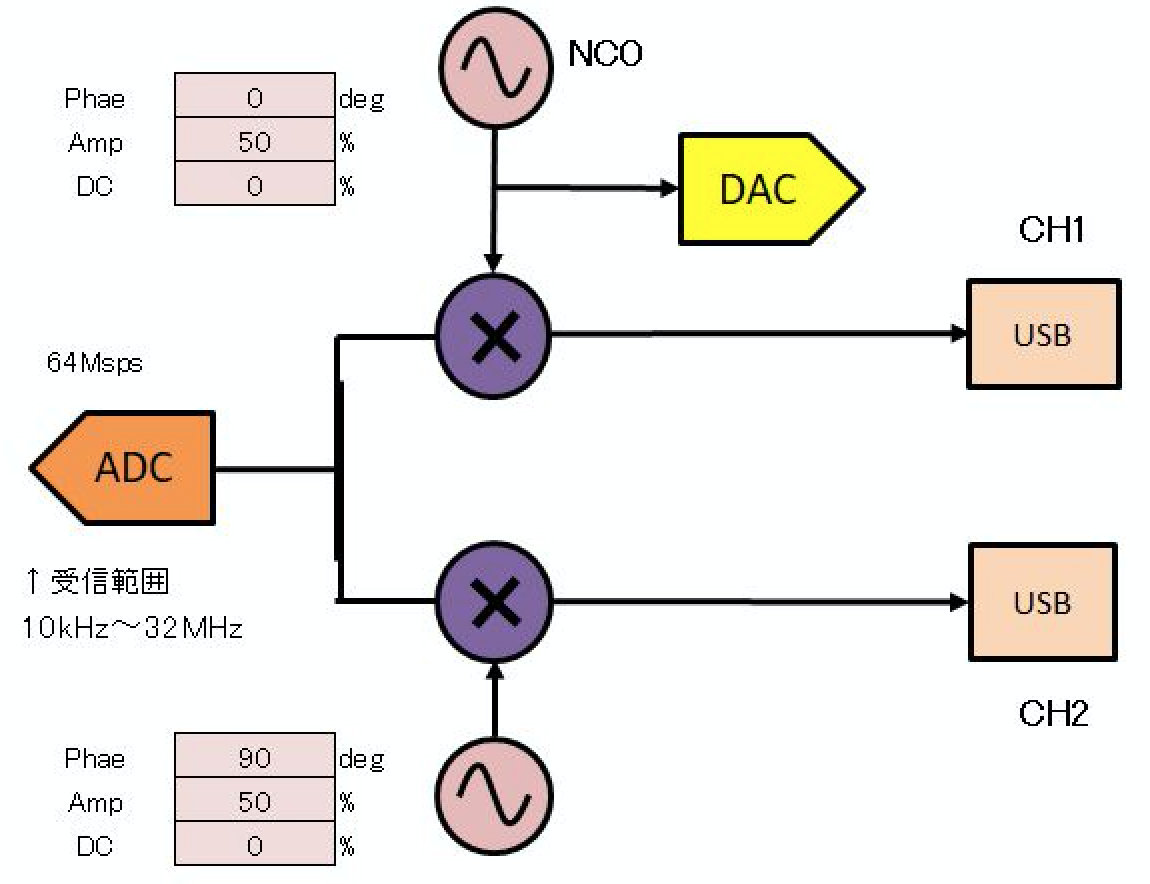

構成例_VNA

フィルタやアンプの通過特性をMag/Phaseで測定できるVNAです。

DACとADCの間に被測定物を接続して使います。実際はADCに60dBのアンプが付いているためDAC出力に40dB以上のATTが必要になります。 CH1、CH2の振幅から位相はPhase=ArcTan(CH1/CH2)、振幅はMag=√(CH1^2+CH2^2)で求められます。