SDR Block HF2

■ご報告■

SBH2ボードの初期ロットにNCO周波数設定で5MHz以上の周波数が正常に出力されないバグが確認されました。 この症状が確認された方は基板をお預りして修正版FPGAを書込致します。

希望される方は radiun.net@gmail.com までご連絡下さい。

SDR Block HFボード(以下SBH1)は大幅な回路変更によりSDR Block HF2(写真上:以下SBH2)へ改版しました。

各種計測機器や短波帯以下の受信機として組み込み対応の引き合いが多かったため、SBH2ではそれら要求に応じた性能や機能の向上を実施しています。

RF初段のローノイズアンプに0〜80dB可変の電圧制御可変ゲインアンプ(VGA)を採用し、A/Dコンバータは10bit(2ch)から14bit(1ch)に変更しています。

この改良によって入力レベル範囲が最大0dBm付近から最小-150dBm以下まで対応、ダイナミックレンジは帯域によりますが70dB以上を確保しています。

このボードはFPGAだけで信号処理装置として成立しますが、その内部回路構成はソフトウェアから瞬時に変更できる特徴を持つ、従来とは異なる発想のSDRボードです。 実現できる回路例は、短波帯以下の受信機、送信機、スペアナ、ネットアナ、オシロスコープ、位相測定など各種計測器、 超音波レーダー、チャープ信号、任意波形発生など各種信号源です。

SBH2ボードの初期ロットにNCO周波数設定で5MHz以上の周波数が正常に出力されないバグが確認されました。 この症状が確認された方は基板をお預りして修正版FPGAを書込致します。

希望される方は radiun.net@gmail.com までご連絡下さい。

SDR Block HFボード(以下SBH1)は大幅な回路変更によりSDR Block HF2(写真上:以下SBH2)へ改版しました。

各種計測機器や短波帯以下の受信機として組み込み対応の引き合いが多かったため、SBH2ではそれら要求に応じた性能や機能の向上を実施しています。

RF初段のローノイズアンプに0〜80dB可変の電圧制御可変ゲインアンプ(VGA)を採用し、A/Dコンバータは10bit(2ch)から14bit(1ch)に変更しています。

この改良によって入力レベル範囲が最大0dBm付近から最小-150dBm以下まで対応、ダイナミックレンジは帯域によりますが70dB以上を確保しています。

このボードはFPGAだけで信号処理装置として成立しますが、その内部回路構成はソフトウェアから瞬時に変更できる特徴を持つ、従来とは異なる発想のSDRボードです。 実現できる回路例は、短波帯以下の受信機、送信機、スペアナ、ネットアナ、オシロスコープ、位相測定など各種計測器、 超音波レーダー、チャープ信号、任意波形発生など各種信号源です。

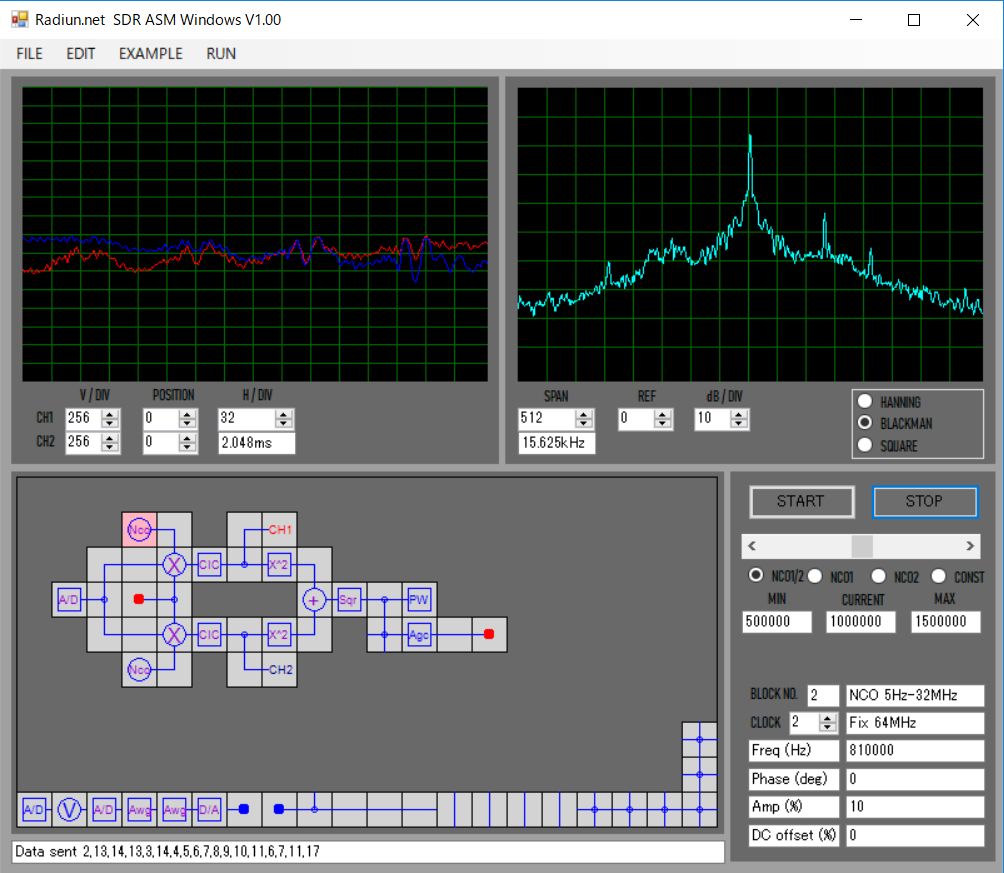

SDR ASM Windowsアプリケーション

従来のSBH1と同じくSBH2もWindows専用アプリケーションでFPGA内部回路の設定が可能です。

電子ブロックのように信号処理回路ブロックを自在に組み合わせて、直ちに動作させることが可能です。 コンパイルもコンフィグも不要ですが、これはシミュレーションではありません。リアルタイムに動作する実際のSDR回路です。

このWindowsアプリケーション「SDR ASM」のVisualStudio C#プロジェクトファイルは公開されており、当サイトからダウンロード可能です。

基本性能

| 代表値 | 備考 | |

| 送受信周波数範囲 | 10kHz〜16MHz | IQ変復調可能なのは8MHz以下 |

| 設定周波数分解能 | 5Hz | NCOの最小分解能 |

| RX ADC x1ch | 14bit 32Msps | LTC1744 max50Msps |

| AF ADC x1ch | 12bit 1Msps | MAX10内蔵 |

| TX DAC x1ch | 10bit 32Msps | DAC900E |

| TX出力 | 差動1Vp-p | 無負荷時 |

| RXゲイン | 86dB | VGA AD8338 0-80dB |

| 回路ブロック数 | 20個 | 2019/11現在 |

| インターフェイス | USB 2.0 | FT232HL 〜12Mbps |

| 電源電圧 | 5V 500mA | USBによる電源供給 |

| 基板サイズ | 75 x 35 mm | DIP 56pin |

ブロック図

SBH1のA/Dは2chの64MHzで動作できましたが、SBH2では1chで32MHzとなっております。 これは同じコストでA/Dの分解能を10bitから14bitに改善するためと、この周波数付近での組み込み用途に16MHz以上の要求があまり無かったためです。

EEPROMはSDRブロックのアプリケーションでは現時点では対応していません。

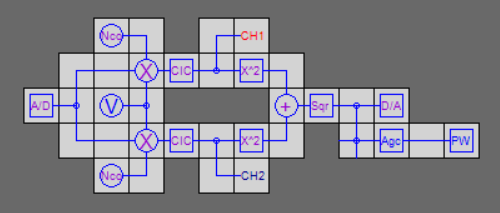

回路例「AMラジオ」

SBH2によるAMラジオの構成例です。SBH1とは異なる点がいくつかあります。

現行のSDR ASM Windows V1.10ではボードの選択はSBH1と同じく「SDR Block HF」ですが、 高速A/Dは2個から1個になったため「Block No14」のみ有効です。 もう片方のA/D「Block No15」には機能がありませんので、ご注意ください。

また「PWM」は音声出力も従来どおり可能ですがVGAのゲイン制御電圧も併用しています。 そのためVGAを使用しつつ音声などアナログ出力が必要な場合は「D/A」を使用してください。

SDRブロックのアプリケーション上では高速A/Dの14bitをそのまま利用できません。12bitのA/DとしてSDR回路ブロックに接続されます。 これはSDRブロックの構造上の制限からマトリックス状の内部信号バスが全て12bitで統一されているためで、一部だけ14bitにしても意味がないためです。

実際の皆様の設計では、SDR回路ブロックの機能を最大限に利用してリアルな信号処理実験を手軽にやっていただき、 動作確認が取れたらVHDLコードを改造して最適化設計を実施することをお勧めします。 例えばCICフィルタの出力は分解能が12bitではなく、更に高い分解能になっているため、それに応じたビット幅のバスに変更します。 A/Dは最大で50Mspsまで、D/Aも100Msps以上まで対応できるため、その速度まで最適化することは可能です。

それらを実施するためにはSBH2のVHDLソースコードが必要ですが、ボード購入者で希望する方にはNCOなど一分機能を除いたSBH2のソースコードを無償で提供致します。 希望する方は弊社へメールで連絡を頂ければ、購入者履歴を確認でき次第ダウンロード方法をお知らせ致します。

CICフィルタはSBH1では4段のCICフィルタだけでしたが、SBH2ではCICの後段に31タップのカットオフ固定FIRフィルタが付いています。 これによりイメージ性能や通過帯域の平坦度を改善していますが、今後の改良でフィルタ係数をPCからアップデートできるようにする予定です。

A/Dコンバータの14bit化に伴いクロックレートを下げたため、全体の最大設定可能クロックを32MHzとしています。 SDR ASMアプリケーション上では64MHzまたは128MHzのクロックを選択可能ですが、32MHz以上のクロックを設定しても全て32MHzとなります。

このサンプル回路は以下でダウンロードできます。

これで受信する音声を聞くとAM放送とは思えないフラットなf特の音質に驚くと思います。

| 名前 | 更新日 | 備考 | リンク |

| AM Radio Sample | 2019/11/15 | SBH2専用サンプル回路 |

SBH2のFPGAが2020/01/22版以降のAMラジオサンプルは以下の通りになります。

変更点はMIXの入力で中央の1ピンが無効になっております。

| 名前 | 更新日 | 備考 | リンク |

| AM Radio Sample | 2020/01/22 | SBH2専用サンプル回路(改) |

信号処理回路ブロック

| 名称 | 個数 | 機能 | 備考 |

| NCO | 2 | 5Hz〜16MHz正弦波発生 | 位相、振幅、DCオフセット可変 |

| MIX | 2 | 乗算回路 | ゲイン調整可能 |

| CIC | 2 | CIC+FIR | デシメーションレート可変 CIC4段+FIR 31tap |

| SQR | 2 | 自乗回路 | 主に絶対値を得るために使用 |

| ADD | 1 | 加算回路 | 2信号加算1信号出力 |

| SQRT | 1 | 平方根回路 | 自乗された信号を元に戻すため使用 |

| V | 1 | 定数発生 | DCオフセット、ゲイン固定値のため使用 |

| AGC | 1 | 自動利得制御 | 時定数可変、積分回路 |

| A/D | 1 | 14bit 32Msps | 最大86dBアンプされた高速・高分解AD |

| A/D | 1 | 12bit 1Msps | MAX10内蔵、オーディオ入力を想定 |

| AWG | 2 | 任意波形発生 | 12bit 4096ワード、サンプリング可変 |

| PWM | 1 | アナログ電圧出力 | 11bit 62.5ksps |

| CH1/2 | 2 | 波形取り込み | ストリームデータ対応 |

| D/A | 1 | 10bit 32Msps | 主に送信、内部波形観測に使用 |

上記回路ブロック20個は全てFPGA内部に組み込まれています。